Faraday Electronics FE3020 Address Buffer

The FE3020 is an 84-pin PLCC chip that forms part of the FE3400B chipset. It handles the address buffering between the 80286 processor and the PC/AT expansion bus.

I don't have a datasheet for this component; the partial pinout described below was discovered by probing a GRiDCase 1520 laptop.

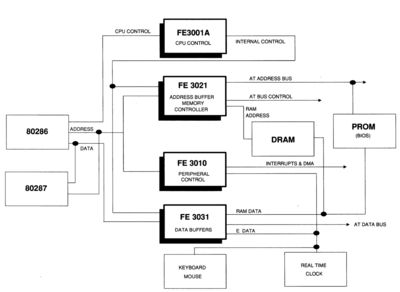

The "FE3001A AT Clock Generation and Cycle Control Device" manual has a block diagram (reproduced below) which references the FE3021 Address Buffer Memory Controller. Of course that's a different, presumably newer, device but it's still a help. The FE3020 appears to be an earlier verson that just does address buffering without the memory controller (the GRiDCase 1520 uses a separate RAMC286 memory controller).

Pin Assignments

| ADD15 | ADD16 | ADD17 | A2 | GND | VCC | ADD18 | A1 | ADD19 | VCC | GND | /SMEMWR | /SMEMRD | /MEMWR | GND | ||||||||||

| 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 84 | 83 | 82 | 81 | 80 | 79 | 78 | 77 | 76 | 75 | ||||

| VCC | 12 | FE3020 | 74 | VCC | ||||||||||||||||||||

| GND | 13 | 73 | GND | |||||||||||||||||||||

| A3 | 14 | 72 | A15 | |||||||||||||||||||||

| ADD14 | 15 | 71 | A14 | |||||||||||||||||||||

| ADD13 | 16 | 70 | A13 | |||||||||||||||||||||

| 17 | 69 | A12 | ||||||||||||||||||||||

| A4 | 18 | 68 | LA20 | |||||||||||||||||||||

| A5 | 19 | 67 | ||||||||||||||||||||||

| A16 | 20 | 66 | ||||||||||||||||||||||

| ADD12 | 21 | 65 | /MASTER | |||||||||||||||||||||

| VCC | 22 | 64 | ||||||||||||||||||||||

| GND | 23 | 63 | /BHE | |||||||||||||||||||||

| ADD11 | 24 | 62 | ||||||||||||||||||||||

| ADD10 | 25 | 61 | HLDA | |||||||||||||||||||||

| A17 | 26 | 60 | ||||||||||||||||||||||

| ADD9 | 27 | 59 | A23 | |||||||||||||||||||||

| ADD8 | 28 | 58 | A22 | |||||||||||||||||||||

| A18 | 29 | 57 | /MEMRD | |||||||||||||||||||||

| A19 | 30 | 56 | /EBHE | |||||||||||||||||||||

| GND | 31 | 55 | GND | |||||||||||||||||||||

| VCC | 32 | 54 | VCC | |||||||||||||||||||||

| 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 50 | 51 | 52 | 53 | ||||

| GND | ADD7 | ADD6 | ADD5 | A20 | A6 | VCC | GND | ADD4 | ADD3 | A21 | A7 | A8 | A9 | VCC | GND | ADD2 | ADD1 | ADD0 | A10 | A11 | ||||

| Pin | Purpose | Direction | Notes |

|---|---|---|---|

| 4, 8, 14, 18, 19, 38, 44, 45, 46, 52, 53, 69, 70, 71, 72, 20, 26, 29, 30, 37, 43, 58, 59 | A1 — A23 | Normally input; output during /MASTER cycle? | CPU address bus. |

| 51, 50, 49, 42, 41, 36, 35, 34, 28, 27, 25, 24, 21, 16, 15, 11, 10, 9, 5, 1 | ADD0 — ADD19 | Normally output; input during /MASTER cycle? | Expansion bus address bus, latched on falling edge of BALE [TechRef 13-5]. |

| 6, 12, 22, 32, 39, 47, 54, 74, 84 | VCC | Power input | +5V DC |

| 7, 13, 23, 31, 33, 40, 48, 55, 73, 75, 83 | GND | Signal ground | Note that pins 33 and 75 are the only ground pins not paired with a VCC pin; they may be signal pins that are strapped to ground. |

| 56 | /EBHE | Output; maybe input on /MASTER cycle? | Provides the Bus High Enable signal that indicates a data transfer on the upper eight bits of the data bus. [TechRef 13-7] |

| 57 | /MEMRD | Maybe input from FE3000A? Can also be driven by expansion bus. | Driven low (active) on all memory read cycles. [TechRef 13-9] |

| 61 | HLDA | Input | Bus hold input from CPU. |

| 63 | /BHE | Input | Bus High Enable input from CPU. |

| 65 | /MASTER | Input | Input from expansion bus used by DMA masters. Presumably causes the FE3020 to tri-state its outputs on the next clock cycle. [TechRef 13-9] |

| 68 | LA20 | Output | Buffered address line 20 output. Not always the same as input A20, as it is conditioned by the A20 gate input. |

| 76 | /MEMWR | Maybe input from FE3000A? Can also be driven by expansion bus. | Driven low (active) on all memory write cycles. [TechRef 13-10] |

| 77 | /SMEMRD | See /MEMRD | Derived from /MEMRD and address decode for lowest 1MB of memory. [TechRef 13-10] |

| 78 | /SMEMWR | See /MEMWR | Derived from /MEMWR and address decode for lowest 1MB of memory. [TechRef 13-9] |

Unknown Pins

| Pin | Notes |

|---|---|

| 2 | Connects to keyboard controller, pin 22. As this is the only connection to the KBC I think this might be the A20 gate input. TODO: check BIOS disassembly to see whether A20 gate goes through KBC. |

| 60 | Connects to RAMC286 chip, pin 13. |

| 62 | Connects to FE3000A, pin 54. |

| 64 | Connects to FE3000A, pin 50. |

| 66 | Connects to FE3000A, pin 61 and RAMC286, pin 20. |

| 67 | Connects to FE3000A, pin 6. |

| 80 | Connects to FE3000A, pin 2. |

| 81 | Connects to BIOS EPROM output enables. |

| 82 | Connects to FE3000A, pin 5. |

| 17, 79 | Connections unknown. |